比利时微电子研究中心(imec)日前发布重大消息,宣布其在高数值孔径极紫外曝光(High NA EUV)单次图形化技术上取得了新的突破性里程碑,代表着High NA EUV图形化能力向A10及更先进逻辑节点迈进的强大实力,同时也强调了Imec在曝光微影技术研发领域的领先地位。

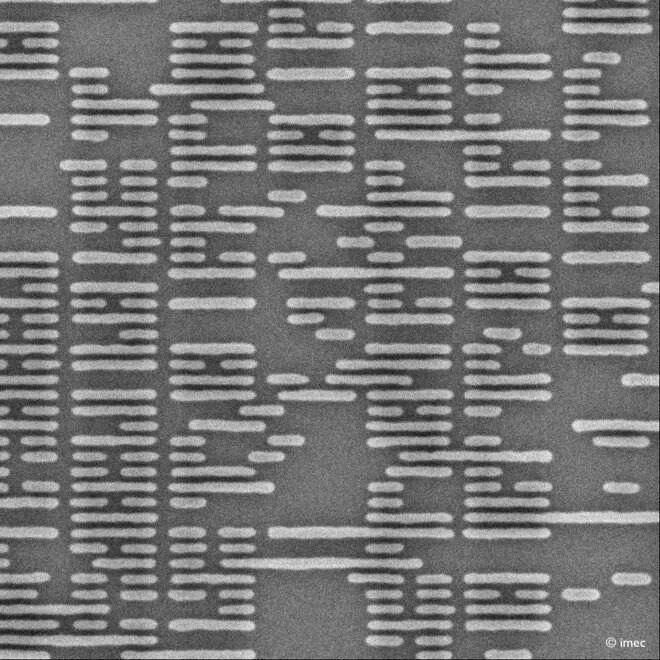

本次成果在2025年SPIE光罩技术+ EUV曝光大会(SPIE Photomask Technology + EUV Lithography Conference)上公开展示,其中包括两项关键突破。 首先,在与镶嵌(damascene)金属化相关的工艺中,成功实现了20纳米间距的线结构,其尖端至尖端(Tip-to-Tip, T2T)临界尺寸(CD)达到了13纳米。其次,透过直接金属蚀刻(Direct Metal Etch, DME)制程,获得了钌(Ru)线路的电性测试结果。

在13纳米T2T临界尺寸结构达成产业里程碑上,过去imec在2025年2月的SPIE先进曝光与图形化会议上展示了20纳米间距金属化线结构。在此基础上,Imec现已透过单次曝光的High NA EUV曝光步骤,成功达成了20纳米间距的线结构,并将尖端至尖端(T2T)的临界尺寸(CD)缩小至13纳米。

在这些13纳米的T2T结构中,所测得的局部CD均匀度(LCDU)低至3纳米,这项数据被视为一项业界里程碑。 imec计算系统扩展高级副总裁Steven Scheer指出,使用单次曝光High NA EUV曝光技术达成这些逻辑设计,相较于多重图形化(multi-patterning)技术,能够减少处理步骤。 这项优势直接带来了降低制造成本、改善良率,以及减少环境影响的多重效益。

这些结支持了互联机制造的行业标准—镶嵌金属化(damascene metallization)。 T2T临界结构是互连层中不可或缺的一部分,因为它们允许中断线性的金属轨道。 为了满足20纳米金属间距的逻辑制程蓝图要求,T2T临界尺寸距离预计必须缩小至13纳米或更小,同时仍需保持功能性互连线路的性能。

目前,imec正持续进行开发工作,以进一步缩小T2T尺寸,并已获得11纳米T2T临界尺寸的良好发展结果。 此外,相关结构正在努力转移至下层硬光罩(underlying hard mask)中,以实现真正的(双)镶嵌互连线。 为了达成这些成果,Imec采用了金属氧化物光阻剂(metal oxide resist, MOR),并与底层、照明瞳孔形状(illumination pupil shape)和光罩选择进行了协同优化(co-optimized)。

然后在直接金属蚀刻(DME)与钌线路的高良率互连方面,随着产业前进到20纳米以下的金属化制程,业界可能需要转向替代性的金属化方案。作为imec的第二项重大成就,他们展示了钌(Ru)的直接金属蚀刻(DME)技术,与单次曝光High NA EUV曝光技术的兼容性。

藉由DME制程,imec成功达成20纳米及18纳米间距的钌线路,其中包括15纳米T2T临界尺寸结构。 这些成果还包括具有低电阻的功能性互连线。值得注意的是,针对20纳米间距的金属化线结构,imec取得了100%的电性测试良率。

imec所取得的重大成果,部分受惠于欧盟的NanoIC测试产线(NanoIC pilot line)的支持。 这些成果不仅标志着High NA EUV单次曝光能力的重要进展,同时也凸显了Imec与ASML之间合作关系的关键作用。

这种伙伴关系对于推动更广泛的生态系统至关重要,该生态系统正在驱动High NA EUV向高量产制造的转型,进而解锁2纳米以下(sub-2nm)逻辑技术蓝图。

Steven Scheer提到,自从位于荷兰费尔德霍芬(Veldhoven)的ASML-imec联合High NA EUV实验室启用以来,Imec及其合作伙伴生态系统在发展High NA EUV曝光方面获得了重大的进展,并将产业推向了埃米时代(angstrom era)。另外,imec所展示的成果标志着一个新的里程碑,再次证实了imec在曝光研发领域的领导地位。这些成就对于达到《欧洲芯片法案》(European Chips Act)中关于推动2纳米以下逻辑节点制程的目标,发挥着关键作用。

imec与ASML High NA EUV生态系统的紧密合作,囊括了领先的芯片制造商、设备供应商、材料和光阻剂供应商、光罩公司以及量测专家。透过与这些伙伴的联合优化,Imec将持续支持逻辑和存储器制程蓝图的进展。